# OPERATOR'S MANUAL MODEL 2108 VXI Serial Data System Digital Resource Module

Manual Revision: 1.0 Revision Date: 10/16/01 Manual Part Number: 2108RM003 Instrument Part Number: 30080/30150/30250

# CERTIFICATION

Talon Instruments certifies that this product met its published specifications at the time of shipment from the factory.

#### WARRANTY

Talon Instruments products are warranted against defects in materials and workmanship as follows:

- (a) One year for the 2108 baseboard and all modules.

- (b) Ninety days for cables and adapters.

During the warranty period, Talon Instruments will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to the Talon Instruments factory. Buyer shall prepay shipping charges to the factory and Talon Instruments shall pay shipping charges to return the product to the Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to Talon Instruments from another country.

Talon Instruments warrants that its software and firmware designated by Talon for use with its instruments will execute its programming instructions when properly installed on the instrument. Talon Instruments does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

# LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. TALON INSTRUMENTS SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. TALON INSTRUMENTS SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

# SAFETY FIRST

# PROTECT YOURSELF AND THE EQUIPMENT

# Follow these precautions:

- Don't bypass the chassis' power cord's ground lead with two-wire extension cords or plug adapters.

- Don't disconnect the green and yellow safety-earth-ground wire that connects the ground lug of the chassis power receptacle to the chassis ground terminal.

- Don't energize the chassis until directed to by the installation instructions.

- Don't repair the instrument unless you are a qualified electronics technician and have instructions from Talon Instruments.

- Pay attention to the **WARNING** statements. They point out situations that can cause injury or death.

- Pay attention to the **CAUTION** statements. They point out situations that can cause equipment damage.

- Use ESD static control procedures when handling the 2108 or any of its modules.

# Table of Contents

| 1.0            | Introduction                                                      |    |

|----------------|-------------------------------------------------------------------|----|

| 1.1            | Basic Elements of Serial Interfaces                               | .6 |

| 1.1.1          | A Set of Electrical Characteristics                               | .6 |

| 1.1.2          | A Logical Protocol                                                | .6 |

| 1.1.3          | Introduction                                                      |    |

| 1.1.4          | Waveform Data                                                     |    |

| 115            | Control Signals                                                   |    |

| 2.0            | Software                                                          |    |

| 2.1            | VXI Plug&Play Software                                            |    |

| 2.1            | 2108 Project Development Software (PDS)                           |    |

| 2.2.1          | Project Development Editor (PDE)                                  |    |

| 2.2.1          |                                                                   |    |

|                | Execution Manager (EM)                                            | .0 |

| 2.2.3          | Serial Logic Analyzer (SLA)                                       |    |

| 2.3            | Software Installation                                             |    |

| 2.3.1          | Maximum System Requirements                                       |    |

| 2.3.2          | Running The Initial Setup Program                                 |    |

| 2.4            | Hardware Installation                                             |    |

| 2.4.1          | Baseboard Switches                                                |    |

| 2.4.2          | Installing the 2108 into the VXI Chassis                          |    |

| 3.0            | Getting Started Using the 2108 Project Development Editor         |    |

| 3.1            | Defining the 2108 Configuration                                   | .9 |

| 3.2            | Routing the 2108TX Signal Pinouts                                 | .9 |

| 3.2.1          | Data Clock                                                        | .9 |

| 3.2.2          | Auxiliary Signals                                                 | 10 |

| 3.3            | Transmitting Data                                                 |    |

| 3.3.1          | Theory of Operation                                               |    |

| 3.3.1.1        | Step 1. Define the Characteristics of the Output Bit              |    |

| 3.3.1.1.1      | Transmitter Panel                                                 |    |

| 3.3.1.1.2      | Drive Module Panel                                                |    |

| 3.3.1.1.3      | Waveform Parameter Registers Panel                                |    |

| 3.3.1.2        | Step 2. Define the Bit Sequence(s)                                | 1/ |

| 3.3.1.2.1      | Control Memory Tables                                             |    |

| 3.3.1.2.1      | Programming Control Memory Tables                                 |    |

|                |                                                                   |    |

| 3.3.1.3        | Examples of CMT's                                                 |    |

| 3.3.1.3.1      | Example 1. Simple 16 Bit One Word Table                           |    |

| 3.3.1.3.2      | Example 2. Two 40 Bit Words with Gap                              |    |

| 3.3.1.4        | Define the Test Sequences                                         |    |

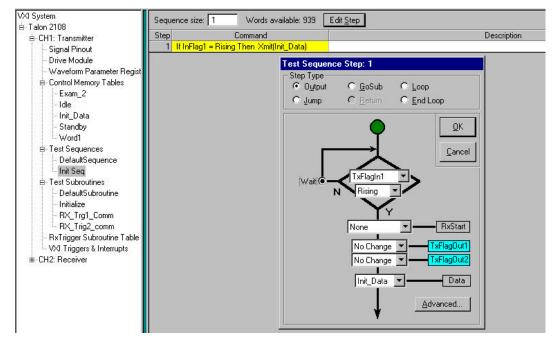

| 3.3.1.4.1      | Programming Sequence Steps                                        |    |

| 3.3.1.4.1.1    | Output                                                            |    |

| 3.3.1.4.1.2    | GoSub                                                             |    |

| 3.3.1.4.1.3    | Jump                                                              |    |

| 3.3.1.4.1.4    | Loop/End Loop                                                     |    |

| 3.3.1.4.1.5    | Sequence Step List                                                |    |

| 3.3.1.4.2      | Test Subroutines                                                  |    |

| 3.3.1.4.3      | RX Trigger Subroutine Table                                       | 21 |

| 3.3.1.4        | Test Sequence Examples                                            | 22 |

| 3.3.1.4.1      | Example 1. Transmitting a CMT When Triggered                      | 22 |

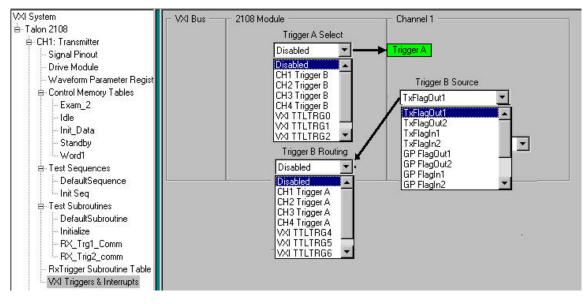

| 3.3.1.5        | VXI Trigger & Interrupts                                          | 22 |

| 3.3.1.5.1      | VXI Triggers                                                      |    |

| 3.3.1.5.2      | VXI Interrupts                                                    |    |

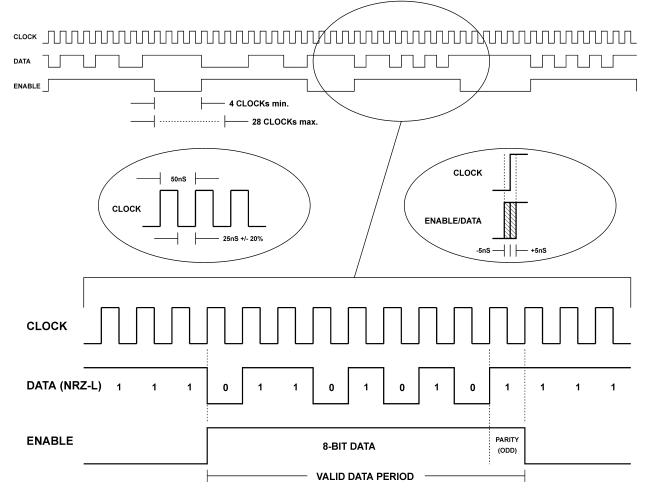

| 4.0            | Characteristics of a Simple Synchronous Serial Bus Interface      |    |

| 4.1            | An Example of a Synchronous Serial Bus Interface                  |    |

| 4.2            | Using the Project Development Software for the Example Serial Bus |    |

| 4.2.1          | Programming the Electrical Characteristics.                       |    |

| 4.2.2          | Programming the Logical Characteristics                           |    |

| 4.2.2          | Programming Data                                                  |    |

| 4.2.3          | Programming a PRBS Data Table                                     |    |

| 4.2.4<br>4.2.5 | Programming the Output Sequence                                   |    |

| 4.2.5<br>4.3   |                                                                   |    |

| 4.3            | Executing a CMT or a Test Sequence                                | 21 |

| Using the 2108RX Receiv      | /er                                                                                                                                                                                                                                                                                | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

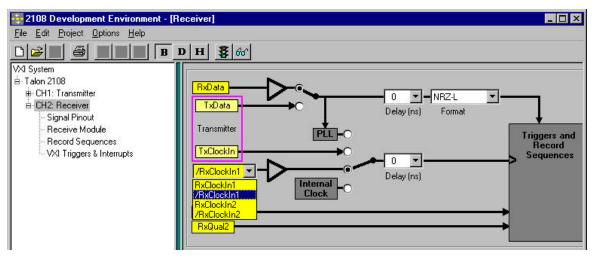

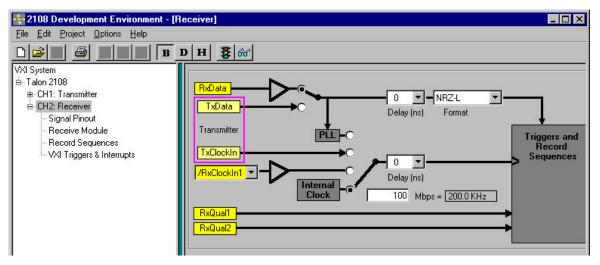

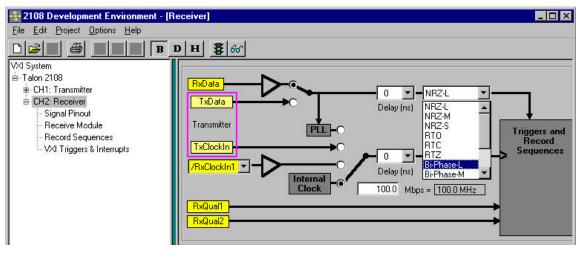

| Step 1. Define the Chara     | acteristics of the Serial Bit                                                                                                                                                                                                                                                      | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| •                            |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

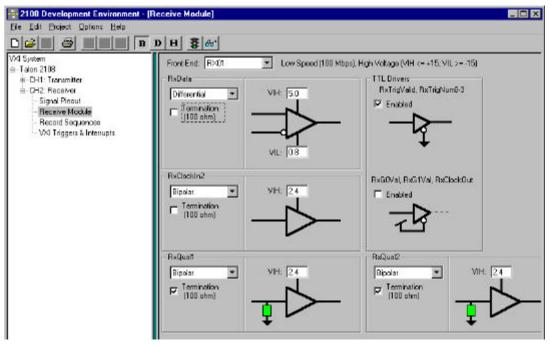

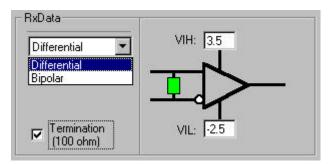

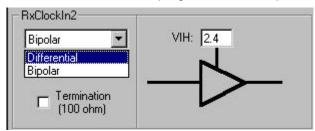

| Receive Module Panel         |                                                                                                                                                                                                                                                                                    | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

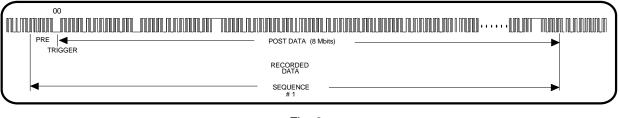

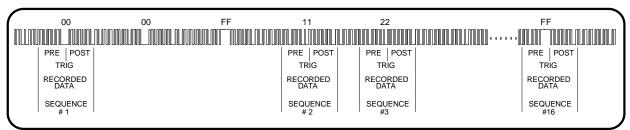

| <b>Record Sequences Pane</b> | l                                                                                                                                                                                                                                                                                  | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Triggering                   |                                                                                                                                                                                                                                                                                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Trigger Registers            |                                                                                                                                                                                                                                                                                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Trigger Example #1: Trig     | ger and Record                                                                                                                                                                                                                                                                     | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Trigger Example #3: Sea      | arch for Multiple Data Values                                                                                                                                                                                                                                                      | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Trigger Example #5: Trig     | ger on Qualifier                                                                                                                                                                                                                                                                   | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Trigger Example #6: Trig     | ger on Waveform                                                                                                                                                                                                                                                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | Routing the 2108RX Sign<br>Theory of Operation<br>Step 1. Define the Chara<br>Receiver Panel<br>Record Sequences Pane<br>Trigger Registers<br>Trigger Example #1: Trig<br>Trigger Example #2: Sea<br>Trigger Example #3: Sea<br>Trigger Example #4: Rec<br>Trigger Example #4: Rec | Using the 2108RX Receiver<br>Routing the 2108RX Signal Pinouts<br>Theory of Operation<br>Step 1. Define the Characteristics of the Serial Bit<br>Receiver Panel<br>Receive Module Panel<br>Record Sequences Panel<br>Trigger Registers<br>Trigger Registers<br>Trigger Example #1: Trigger and Record<br>Trigger Example #2: Search for a Sequence of Data Values<br>Trigger Example #3: Search for Multiple Data Values<br>Trigger Example #4: Record a Multiple Number of Words<br>Trigger Example #5: Trigger on Qualifier<br>Trigger Example #6: Trigger on Waveform |

~

#### 1.0 INTRODUCTION

The Model 2108 is a flexible and capable serial bus emulator module that can be programmed to emulate a vast variety of serial bus protocols at speeds from 2kBps to 200MHz data rate. The flexibility of the 2108 module allows the user to fine-tune virtually all aspects of a serial bus interface, both at the electrical and logical levels.

The Model 2108 is comprised of a "C" size VXI motherboard which houses four instrument modules and four front-end signal conditioning modules. For serial emulation the instrument modules are the transmitter, 2108TX and the receiver, 2108RX . A number of front-end modules for the 2108TX and 2108RX are available to provide signal conditioning for the various requirements imposed by different interfaces.

The Model 2108 may be configured with 1-4, 2108TX's, 1-4, 2108RX's or a combination of the two. If a 2108TX and 2108RX are installed in channel slots 1&2 or 3&4 they may be operated in a bi-directional mode.

#### 1.1 BASIC ELEMENTS OF SERIAL INTERFACES

There are a variety of serial interfaces being used today in the consumer, industrial and military sectors. Although a significant percentage of these interfaces are comprised of a number of standardized serial protocols, such as USB, IEEE 1394 and MIL-STD-1553, there is still an equally large percentage composed of custom serial interfaces. This group includes not only purpose-built interfaces but also variants of the standardized protocols.

In all instances, these standard and custom serial interfaces share some very basic elements. These elements include a set of electrical characteristics, a logical protocol and a method of clocking the data. In addition, some serial buses require special waveforms and control signals. The Model 2108 provides the resources in a programmable format to meet the physical and logical characteristics of most interfaces.

#### 1.1.1 A SET OF ELECTRICAL CHARACTERISTICS

The data bit is the very building block of any serial transmission and assumes physical properties that must be defined to suit a particular protocol. The Model 2108 provides the following programmable resources to define the serial bus electrical characteristics:

- a) Signal Type- differential, bi-polar or trinary

- b) Voltage Levels various levels from ECL, LVDS, TTL, +/-15Vdc, etc.

- c) Slew Rate min. 0.15V/ns to a max. 3V/ns

- d) Termination may be programmed on or off

The Model 2108 transmitter enables the user to set not only the default electrical characteristics of the bit, but also a second set which may be used to create "error" states.

#### **1.1.2** A LOGICAL PROTOCOL

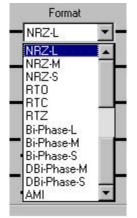

After the data bit is defined as an electrical entity, the logical protocol decides how that entity will represent logical data in the context of a serial transmission. Bit formats such as NRZ-L represent a logical "1" with a corresponding voltage "high" level and a logical "0" with a voltage "low" level. Variations of the Bi-Phase format equate either the rising or falling edges of the data pulses with a logical "1" or a logical "0", depending upon the particular variant. The Model 2108 supports all of the popular bit formats, such as:

- a) Non-Return Level, Mark or Space

- b) Return One, Compliment or Zero

- c) **Bi-Phase** Level, Mark or Space

- d) **DBi-Phase** Mark or Space

- e) AMI Alternate Mark Inversion

In addition to the bit format, bit ordering during a transmission is also determined by the protocol. This order can be either LSB (Least Significant Bit) or MSB (Most Significant Bit) first.

Parity generation is calculated "on-the-fly" and the Model 2108TX allows the user to insert the parity bit on a word or frame basis.

#### 1.1.3 INTRODUCTION

The Model 2108 provides internal clock sources for each channel which supports data rates from 5kbps to 200Mbps. Additionally, the user may also select to clock the channels from external sources at the 5kbps to 200Mbps rates. In addition the 2108RX receiver may be phase locked to the external clock or to the received data.

#### 1.1.4 WAVEFORM DATA

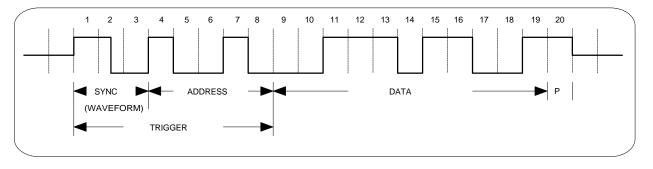

Some serial buses require data which cannot be generated using logical ones and zeros to be output as part of a data stream. This data is usually referred to as "invalid bit format". The Model 2108TX transmitter provides register space to define up to 4 waveforms from 2 to 12 clock periods in length that may be inserted in serial data streams. There is an additional register memory for defining up to 4 waveforms of 2 clock periods which are used to generate word or frame gaps. The 2108RX receiver's trigger logic may be programmed to recognize and trigger on waveform data as well.

#### 1.1.5 CONTROL SIGNALS

In addition to clock and data signals some serial buses require separate signals for sync, enables and triggering. The Model 2108 provides 8 input/output signals in addition to the clock and data lines for emulating complex serial interfaces or to synchronize with other instruments in the test system. These signals are:

| a) Markers (2)            | Output from the Model 2108TX, these signals may be programmed in sync or 1-<br>3 bit times prior or following the first and last data bits of a word or frame.                                                                   |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b) Output Flags (2)       | Output from the Model 2108TX, these signals are pulses and can be used to trigger the UUT or other instruments in the test system. They are sync'd to the first bit of a word or frame and remain true until the word is output. |

| c) Strobe (1)             | Output from the Model 2108TX, this signal can be used to sync to the data bits or as a clock in bi-phase format applications.                                                                                                    |

| d) Sync Pulse (1)         | Output from the Model 2108TX, this signal may be programmed to start at a bit and remain true for up to 16 bits.                                                                                                                 |

| e) Input Flags (2)        | Input to the Model 2108TX, these signals may be used to start execution of a data stream or word from the Model 2108TX Transmitter.                                                                                              |

| f) Receiver Triggers (16) | Input to the 2108TX from the 2108RX, each trigger may be used to start execution of a unique data table.                                                                                                                         |

| g) Qualifier Signals (2)  | Input to the Model 2108RX, tests for High or Low to trigger recording.                                                                                                                                                           |

| h) Pattern Triggers (16)  | Up to 16, 32 bit wide patterns may be used to set 1 of 16 triggers to start recording of data by the 2108RX and output from the 2108TX.                                                                                          |

# 2.0 SOFTWARE

The Model 2108 is shipped with two sets of software. The first is a fully functional set of VXIPlug&play drivers including a Soft Front Panel. The second is a user application package referred to as the 2108 Project Development Software.

#### 2.1 VXIPLUG&PLAY SOFTWARE

### 2.2 2108 PROJECT DEVELOPMENT SOFTWARE (PDS)

The 2108 PDS is a comprehensive application package that provides the user with easy to use graphical programming tools to develop set-up files, execute tests and view the recorded data. The package contains 3 distinct application programs to provide the majority of users with all the necessary functions to develop a functioning serial interface. It was developed for the Windows environment and operates on Win95, 98, 2000, or NT based systems.

### 2.2.1 PROJECT DEVELOPMENT EDITOR (PDE)

The Project Development Editor is the basic application program. It provides the resources to program the logical and physical characteristics of a serial interface. In addition it provides the tools to program data tables and test sequences for stimulating the Unit Under Test, (UUT). Record triggers based on unique start patterns are also easily programmed using the 2108RX receiver's GUIs. Files created by the PDE are saved and may be downloaded using the VXI drivers or the Execution Manager.

#### 2.2.2 EXECUTION MANAGER (EM)

The Execution Manager application provides an interactive link to download set-up files from the VXI controller to a Model 2108. In addition it allows the user to select and run any test sequences defined using the PDE. The user may loop from 1 to 32k times or run in continuous mode to aid in program debugging. 2108RX receivers may be "armed" using the EM.

# 2.2.3 SERIAL LOGIC ANALYZER (SLA)

The Serial Logic Analyzer application provides an interactive means of uploading recorded data from the 2108RX receiver. The data may be viewed as "raw" data or segmented by bit count, labeled and displayed as binary, hex, decimal or ASCII. This decoded data display is accomplished by defining templates that may be saved as a file. The template file may be applied to interactively recorded data when using the Execution Manager or used to analyze data recorded over a period of time. The SLA also provides search functions which operate on raw or decoded data or the label.

#### 2.3 SOFTWARE INSTALLATION

The VXI drivers as well as the Project Development Software are contained on a CD Rom which is shipped with each Model 2108 ordered. The software may be installed on as many systems as will be used to program or control the Model 2108. The software may be distributed as part of a system shipped by Talon's customer without restriction.

#### 2.3.1 MINIMUM SYSTEM REQUIREMENTS

- IBM-compatible PC with CD-Rom Drive

- Windows 95, 98, 2000, ME, or NT

- 64M+ RAM recommended

- Windows® compatible mouse or other pointing device

#### 2.3.2 RUNNING THE INITIAL SETUP PROGRAM

Windows® Autoplay feature will automatically start the setup program. If Autoplay is not enabled, follow the steps below to run the setup program.

2108

Developme...

- 1. Click on the Start Menu and choose <u>R</u>un.

- 2. Type D:\setup.exe and press Enter. If the CD-Rom drive is not drive D, substitute the correct drive letter for the D:.

- 3. The menu program for the disc will start and an opening screen will appear. Click the <u>N</u>ext button to proceed and follow the instructions on the screen.

#### 2.4 HARDWARE INSTALLATION

After unpacking the Model 2108 visually inspect the unit for any obvious shipping damage. If any damage is noted, contact Talon Instruments immediately for advice on how to proceed.

#### 2.4.1 BASEBOARD SWITCHES

There are two switches the user needs to check and possibly set for his system prior to installing the Model 2108 into the VXI chassis. These switches and their setting are described Section 3.1 of the Model 2108 Reference Manual.

#### 2.4.2 INSTALLING THE 2108 INTO THE VXI CHASSIS

The Model 2108 may be installed in any slot other than the Slot 0 position. It should be inserted firmly but without undue force. When properly seated the front panel will be flush against the chassis card cage and the tightening screws may be used to hold the module firmly.

# 3.0 GETTING STARTED USING THE PROJECT DEVELOPMENT EDITOR

The Soft Front Panel may be used to determine if the Model 2108 is up and operational. Click on the 2108sfp.exe icon or run the file to start. The software will search for installed 2108 modules and report with the logical addresses.

#### 3.1 DEFINING THE 2108 CONFIGURATION

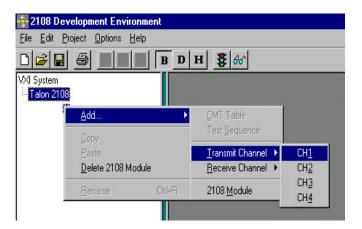

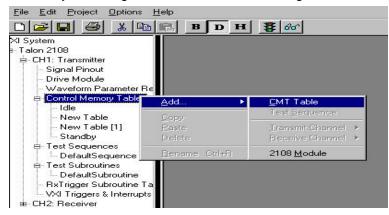

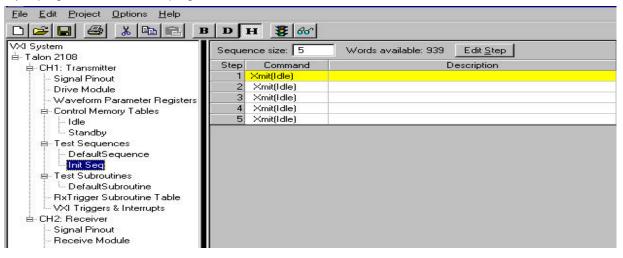

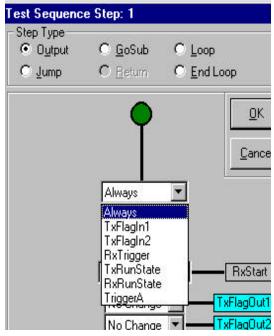

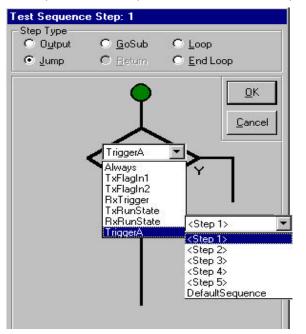

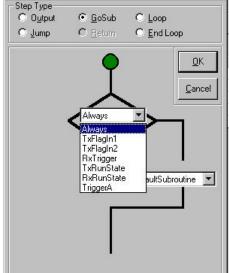

The first step in using the PDE is to configure the 2108 (s) being programmed by defining the number and type of instruments installed in each channel slot. After starting the program, right click on VXI System in the menu directory to add a model 2108 module. Right click on the Talon 2108 module being programmed to add either Transmit or Receive channels or additional 2108 modules. See fig. below.

# 3.2 ROUTING THE 2108TX SIGNAL PINOUTS

The 2108TX has multiple signals which may or may not be needed for the serial interface being programmed. The I/ O modules have access to all the 2108TX signals but only a limited number may be output due to the limited number of programmable drivers on the standard I/O modules (TX01 and TX02). Custom I/O modules could be designed with enough drivers to output all signals and would not require the use of the Signal Pinout directory menu.

# 3.2.1 DATA AND CLOCK

The TxData and TxClockOut signals are always output on pins 2A and 4A if bi-polar mode is selected. If differential is selected then TxData will be on pin 2A and /TxData will be on pin 4A. Grounds will always be on the odd pins be-

tween signals.

#### 3.2.2 AUXILIARY SIGNALS

The user selects the signals he needs for his interface and routes them to the selected pins using the pulldown selections in the Assigned Signals column. The user may also elect to enter names in the UUT and Description columns for documentation purposes.

|                             | BD         | H 3 60      |                                          |            |                                                                     |

|-----------------------------|------------|-------------|------------------------------------------|------------|---------------------------------------------------------------------|

| System                      | Pin        | Connector   | Assigned Signal                          | UUT Signal | Description                                                         |

| Talon 2108                  | 24         | TeSig1      | TeData                                   | 1 (H)      | Data                                                                |

| - CH1: Transmitter          | <b>4</b> A | TaSig2      | /TsDala                                  |            | Dato complement                                                     |

| Drive Module                | 6,4        | TaSig3      | TriClockDut                              |            | Clock out                                                           |

| Waveform Parameter Regist   | 8,4        | THSig4      | /TiClock0ut                              | 343        | Clock Complement                                                    |

| the Control Monicay Tables  | 104        | THSIG5      | TsMarkert                                | 343        | Enable                                                              |

| I Test Sectionces           | 135        | THSIG6      | /TirNarker1                              | 343        | Enable Complement                                                   |

| # Test Subroutines          | 145        | TuSig7      | TaFlagDut1                               | 343        | Trigger                                                             |

| RikTrigger Subroutine Table | 164        | TaSigB      | TaSyncPulse                              |            | Sync Pulse                                                          |

| VXI Treggers & Interrupts   | 20         | TrFlagint   | C. C |            | <ttl 1="" flag="" input=""></ttl>                                   |

| e CH2: Piecetver            | 40         | TaPlagin2   |                                          |            | <ttl 2="" flag="" input=""></ttl>                                   |

|                             | 60         | TxClockin2+ |                                          | 340        | <programmable clock="" input-<="" positive="" td=""></programmable> |

|                             | 88         | TsElockin2- |                                          | 343        | <programmeble clock="" input)<="" negative="" td=""></programmeble> |

|                             | 108        | TaBuny      |                                          | 343        | <ttl autout="" burg="" trenamitter=""></ttl>                        |

|                             | 128        | TaSyncPuter |                                          | 340        | <ttl pulses-<="" sync="" td="" transmitter=""></ttl>                |

|                             | SMA        | TeCkellnt   |                                          | 12 14      | (High speed ECL input clock)                                        |

#### 3.3 TRANSMITTING DATA

The 2108TX module provides the necessary resources to output data in a serial stream using different formats, protocols, data rates, etc. It also provides auxiliary signals such as a shared clock, markers, sync, triggers, etc., required by many serial interfaces.

#### 3.3.1 THEORY OF OPERATION

The operation of the 2108TX requires the user to define the characteristics of the serial interface to be emulated. This includes data to be output and the sequence in which the user wants the data output. It is best if the user follows a logical sequence in setting up a transmit routine. We recommend the user follow the steps listed below:

#### 3.3.1.1 STEP 1. DEFINE THE CHARACTERISTICS OF THE OUTPUT BIT

Serial data is transmitted as a stream of bits. These bits may be expressed in many formats, Non-Return, Return, Bi-Phase, etc. The bit characteristics of the serial interface are programmed using three panels of the PDE. The three panels are, Transmitter, Drive Module and Waveform Parameter Registers.

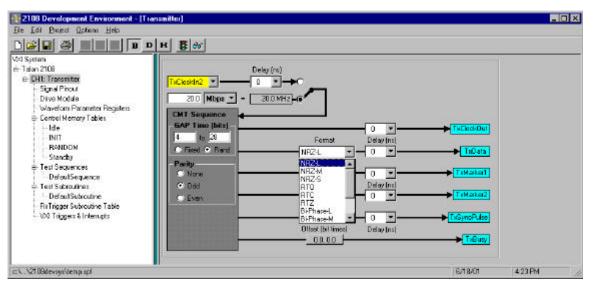

#### 3.3.1.1.1 TRANSMITTER PANEL

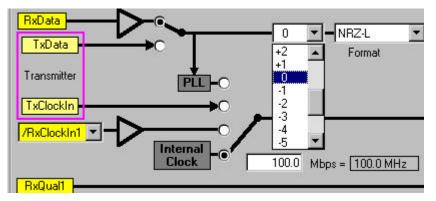

The logical Bit characteristics are programmed using the Transmitter Panel. In the Transmitter Panel the user programs:

| NAME AND ADDRESS OF TAXABLE PARTY OF TAXABLE PARTY OF TAXABLE PARTY.                                                                                                                                                                                                                             | B D H S 66 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MI System<br>⇒ Taken 2108<br>⇒ ERIT Transmitted<br>Signal Prinout<br>– Drive Medule<br>– Waretom Parameter Registers<br>⇒ Cantrol Menogr Tables<br>– Hote<br>– Standby<br>⇒ Teel Sequences<br>– Detsuff signature<br>– Detsuff signature<br>– Detsuff signature<br>– Mit Traggers II: Interrupts | TuCkokin20 | 20 (ht)<br>10 DMHz<br>Formel<br>0 elsy (nt)<br>0 met (bit fames)<br>0 met (b |  |

1) Clock Source- external or internal clock sources may be selected as the transmitter master clock

|               | Delay (ns) |

|---------------|------------|

| TxClockIn1 💌  |            |

| 10.0 Mbps - = | 10.0 MHz   |

2) Bit Rate- bit rates from 2kBps to 200MBps may be entered.

| 10.0    | Mbps 💌       |

|---------|--------------|

| CMT Seq | Mbps<br>Kbps |

3) Bit Formats- the required bit format may be selected from a pull down selector

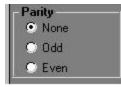

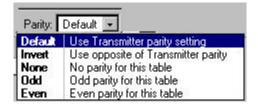

4) Parity- parity if required is set as None, Odd or Even

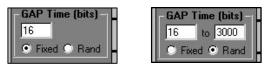

5) Gap- gap times may be set to fixed or random with limits from 4 to 65k bit times

1 1

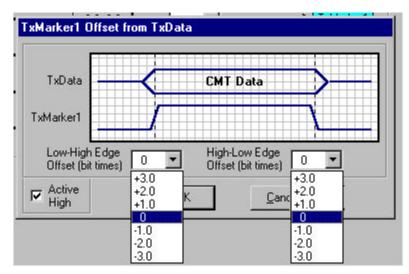

6) Marker Signal(s)- may be set to operate coincident with the data or +/- 3 clocks from the active data and active high or low

7) **Delay**- delays in 1ns increments from +/- 10ns may be programmed to most signals when cable or UUT delays cause synchronization problems

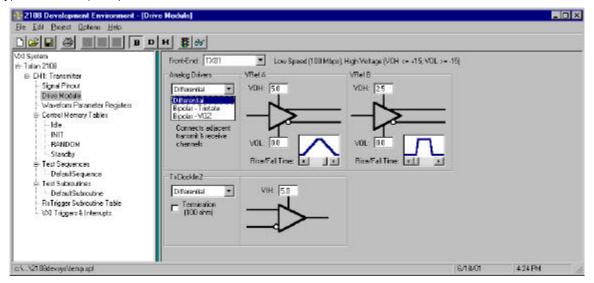

#### 3.3.1.1.2 DRIVE MODULE PANEL

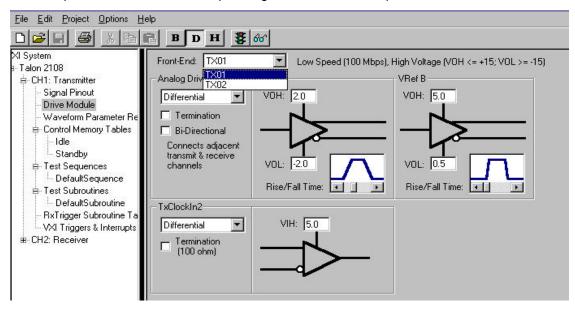

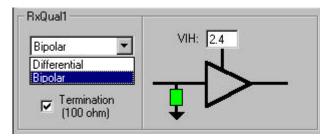

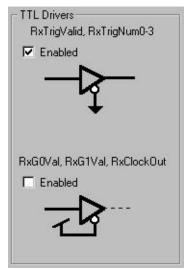

The physical bit characteristics refer to the voltage and signal type along with termination. The signals are a function of the I/O module and are programmed through the Drive Module panel. Review the manual for the specific I/O module for complete signal definitions and specifications.

The signal characteristics to be programmed are:

1) Signal Type- the selections for most I/O modules include Differential, bi-polar with tri-state or bi-polar with a third state (trinary)

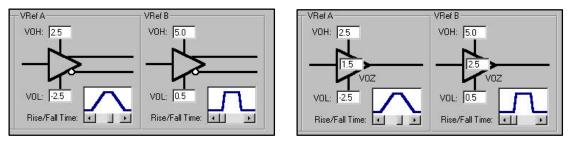

**2)** Signal Voltage – VrefA is the primary voltage reference requiring the output levels VOH and VOL to be entered, (3<sup>rd</sup> voltage if Bi-polar VOZ is selected), slew rate is selected by use of the slide bar window (Rise/Fall Time); VRefB may be used as a secondary voltage reference to generate errors or as a margining voltage reference

**3)** Termination- most of the I/O modules allow the selection of terminated or un-terminated signals.

**4) TxClockIn2**- if using external clock 2 as Clock Source the "signal good" level is programmed in this window for differential or bi-polar along with the termination choice

**5) Bi-directional-** if selected the transmitter I/O module will be the only connection to the interface bus and incoming data will be routed to the adjacent 2108RX module for bi-directional operations

#### 3.3.1.1.3 WAVEFORM PARAMETER REGISTERS PANEL

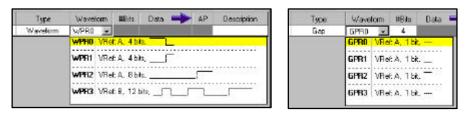

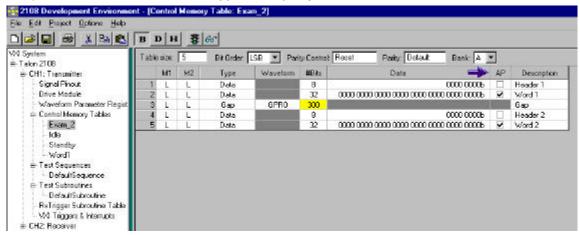

The third aspect to bit definition is the requirement to use waveforms for data representation. Some biphase buses use non-logical bit patterns for sync codes. For example, the military 1553 bus has a Command Word sync code which is a signal represented as 1½ bit times high followed by 1½ bit times low. Another bus needs a pulse stream where 2 bits low out of 8 is a zero and 6 bits low out of 8 is a one. These waveform are programmed via the Waveform Parameters Register panel. There are two types of waveform registers:

**1) Waveforms**- 4 custom waveforms (WPR0, WPR1, WPR3 & WPR4) may be defined as using Voltage Reference A or B, the number of bit times (4 to 12 bits), and the waveform. Waveforms are programmed by selecting a cell and clicking or entering an L or H to set desired state, (biphase selections allow ½ bit time selections between 2 & 12 bits).

| Net | HBA                | 1                 | 2                 | 3                                       | 4 | 5 | 6                                       | .7                                      | 8                                       | 9                                       | 10               | 11  | 12 | 11                                      |                                                | Vief. | #8its                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   | 2    |     | 3   | 4   | 5    | 6   | 7                                                                                                         | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -11 | 12                                      |

|-----|--------------------|-------------------|-------------------|-----------------------------------------|---|---|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|------------------|-----|----|-----------------------------------------|------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-----|-----|------|-----|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------|

| A   | 4                  | -                 |                   | _                                       |   |   |                                         |                                         |                                         |                                         |                  |     |    |                                         |                                                | A     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |      |     |     |     |      |     |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                                         |

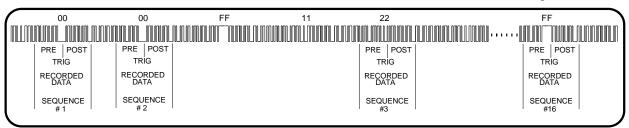

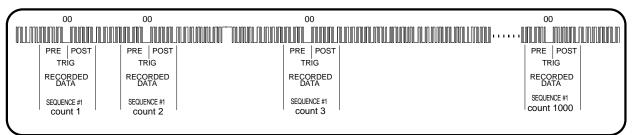

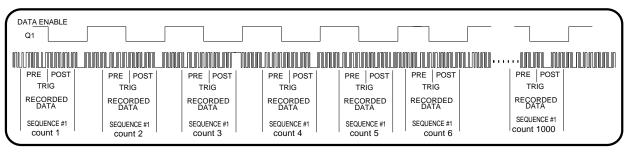

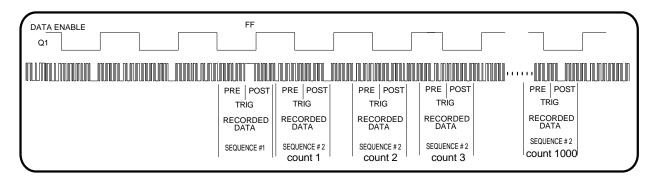

| A   | 8                  |                   |                   |                                         |   |   |                                         |                                         |                                         |                                         |                  |     |    | Ш                                       | WPR1                                           | A     | з                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 1    | 1   |     |     |      |     |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                                         |